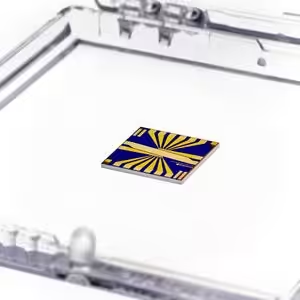

GFET-S20P for Sensing applications

Call for Price

- Growth method: CVD synthesis

- Polymer assisted transfer

- Chip dimensions: 10 mm x 10 mm

- Chip thickness: 525 μm

- Number of GFETs per chip: 12

- Gate oxide thickness: 90 nm

- Gate oxide material: SiO2

- Resistivity of substrate: 1-10 Ω.cm

- Metallization: Au contacts

- Graphene field-effect mobility: >1000 cm2/V.s

- Encapsulation: ≈200 nm glutarimide-based

- Dirac point (liquid gating): <1V

- Minimum working devices: >75 %